## Comparison of multicarrier PWM techniques for ninelevel inverter drive an open-end winding induction motor

#### Ali K. Abdul- Abbas

Department of Electrical Engineering College of Engineering -Basra University ali univbasra75@yahoo.com

Abstract- Different modulation techniques of Nine-Level Inverter (NLI) for an Open-End Winding Induction Motor (OEWIM) is presented in this paper. The two five-level inverters are fed by both ends of open-winding induction motor. The five-level inverters are connected by cascading of four two-level inverters. This inverter topology does not neutral-point fluctuation so this topology different from neutral-point clamping inverter and this scheme does not the diode clamping to fixed neutral point. In the different multilevel sinusoidal pulse width modulations used for the proposed topology. The drive is implemented and simulation with an open-end winding induction motor and simulation results are presented.

Index Terms- nine-level inverter, multicarrier PWM, open-end winding I.M.

#### I. Introduction

They can lessen the strain on the switching devices as higher levels are compositing from voltage sources with lower levels by using multilevel inverter[1]. There are three main configuration of multilevel inverters for high power induction motor drive: the neutral-point clamping inverters[2], cascade H-bridge inverters[3] and dual inverter fed open winding induction motor drives[4].

The neutral-point clamped inverters suffer neutral-point fluctuations as the DC-link capacitors have to take the load current[5]. The cascade multilevel structure has been drive for induction motor and it demand major DC power supply for all three phases, which raise the power circuit elaboration, supply the open-end winding motor from both ends also make in a multilevel inverter[6].

A sine-triangle PWM and a space vector generation are utilize for drive two OEWIM by using VSI for an open-end winding induction motor drive[7].

In this paper, a multilevel voltage space vector generation, equivalent to a conventional nine-level inverter is given for an OEWIM drive using two five-level inverters. The five-level topology utilized is realized by cascading four two-level inverters. This nine-level inverter does not neutral point fluctuation and uses a least number of DC sources compared to the cascade multilevel inverter topology. In various modulation of the multilevel sine-triangle PWM perform for the drive OEWIM are given to the modulating wave depending on the speed range resulting in lessen switching losses and in lessen switching of the inverter.

# II. Open-End Winding Induction Motor (Oewim)

The open-end winding structure of the induction motor system is take out by opening the neutral point of the stator winding in a three-phase induction motor[8]. The winding in each phase will be preserved open and the each phase ends a, b, c, and a', b', c' are fed with individual inverter.

This structure is best for high power application. The advantages of OEWIM are obscurity of neutral point fluctuation , reduced THD value and low dv/dt at output voltage.

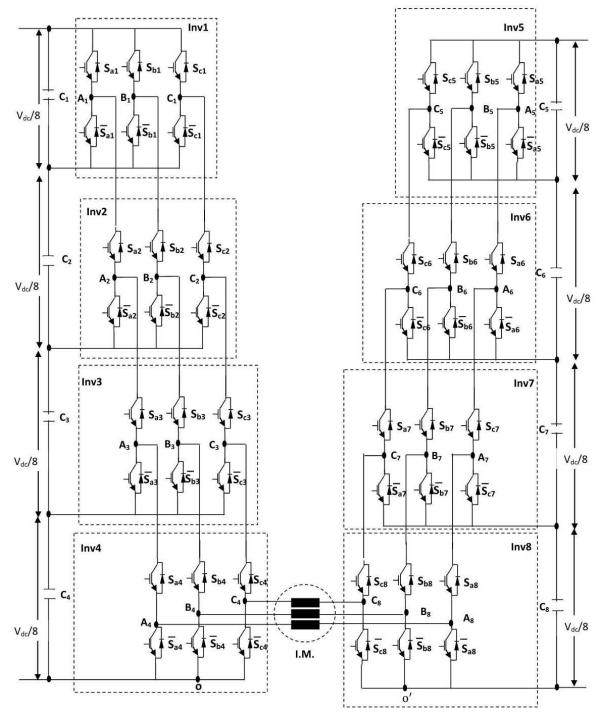

#### III. Proposed Topology Of Inverter

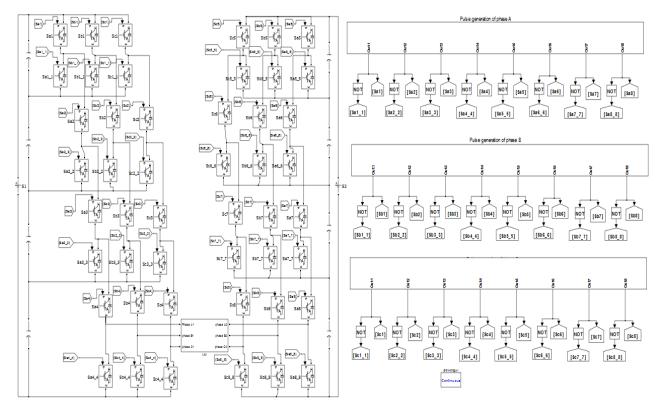

The topology of the proposed drive with open-end winding induction motor is shown in Fig. (1). Both ends of induction motor is fed by two five-level inverters, inverter I and inverter II. These five-level inverters are realized by cascading four two-level inverters. Inverters I is realized by cascading four inverters Inv1, Inv2, Inv3 and Inv4 and inverter II is realized by cascading four inverters Inv5, Inv6, Inv7 and Inv8. All eight two-level inverters have a separate DC supply voltage of  $V_{dc}/8$  where  $V_{dc}$  is the DC-link voltage of the classical two-level inverters fed induction motor drive.

### IV. Operation Of Five-Level Inverter

The pole voltages  $\mathbf{v_{A4o}}$ ,  $\mathbf{v_{B4o}}$  and  $\mathbf{v_{C4o}}$  of inverter I can realized five-level voltages 0,  $V_{dc}/8$ ,  $V_{dc}/4$ ,  $3V_{dc}/8$ , and  $V_{dc}/2$ . Inverter II is also five-level inverter and its pole voltage with respect to the neutral point  $\mathbf{o'}$  ( $\mathbf{v_{A8o'}}$ ,  $\mathbf{v_{B8o'}}$ , and  $\mathbf{v_{C8o'}}$ ) can independently form of the five-level voltages 0,  $V_{dc}/8$ ,  $V_{dc}/4$ ,  $3V_{dc}/8$ , and  $V_{dc}/2$ . When these five-level inverters drive the induction motor from both sides, each phase can generation

nine different levels. To realized the equivalent levels when inverters I and II are operated independently, we assume that the two points o and o' are connected. The phase voltages are given by

$$v_{A4AB} = v_{A40} - v_{AB0'} \tag{1}$$

$$v_{B4B8} = v_{B40} - v_{B80}' \tag{2}$$

$$v_{C4C8} = v_{C40} - v_{C80'} \tag{3}$$

Fig.1 Structure of the nine-level inverter.

The nine-levels realized in the A-phase when inverters I and II are switched with different pole voltage levels are given in Table (1).

The first four levels ( $-V_{dc}/2$ ,  $-3V_{dc}/8$ ,  $-V_{dc}/4$  and  $-V_{dc}/8$ ) are obtained when inverter I is clamped to zero and while inverter II is operation in voltage levels  $V_{dc}/2$ ,  $3V_{dc}/8$ ,  $V_{dc}/4$  and  $V_{dc}/8$ , respectively. At the speed lightest operation, only inverter II will be operation and the speed highest operation, the inverter I will be operation.

These voltage levels in any phase can be obtained by turning 'ON' both switches in inverter I and inverter II. Table 2 shows all combination the A-phase winding. Whenever the topmost switch in any leg of the undermost inverter is ON, the higher switches in the same leg of the topmost inverter is kept OFF so that it has to DC voltage blocking across switch in topmost inverter is  $V_{\text{dc}}/8$ . So

selected only one of the combination switches in each case in Table 2 ( the row misleading). The undermost switches of the inverters Inv4 and Inv8 have to be rated for  $V_{dc}/2$ , so blocking  $V_{dc}/2$  when the uppermost switches of inverters Inv1, Inv2, Inv3,Inv5, Inv6, and Inv7 are 'ON' (case E in Table 2).

This inverter topology does not need any clamping diodes as in the case of neutral diode clamping inverter. So the DC-link capacitor do not carry any load current and hence the neutral point swing are missing. When compared with the cascade connected H-bridge, it uses the same count of switching but use fewer DC power supply as the cascade H-bridge will need twelve DC power supplies.

#### V. Voltage Space Vector Of Suggest Scheme

The complex effect of the three phase voltage in the three phase winding of the induction motor at any moment could be perform by an equivalent space vector v<sub>s</sub> as

$$v_{s} = v_{A4AB} + v_{B4BB}e^{j(-\frac{2\pi}{3})} + v_{C4CB}e^{j(\frac{2\pi}{3})}$$

(4)

Substituting equations for the voltages as given by (1) to (3)

$$v_{s} = (v_{A40} - v_{A80'}) + (v_{B40} - v_{B80'})e^{j(-\frac{2\pi}{3})} + (v_{C40} - v_{C80'})e^{j(\frac{2\pi}{3})}$$

$$(5)$$

This vector can be resolve the phase voltage into two orthogonal axes, the  $\alpha$  and  $\beta$  axes, the  $\alpha$ -axis is along the Aphase axis

The space phase v<sub>s</sub> as following

$$\mathbf{v}_{\mathbf{s}} = \mathbf{v}_{\mathbf{s}\alpha} + j\mathbf{v}_{\mathbf{s}\beta} \tag{6}$$

$\mathbf{v}_{s\alpha}$  and  $\mathbf{v}_{s\beta}$  are given by

$$v_{s\alpha} = v_{A4A8(\alpha)} + v_{B4B8(\alpha)} + v_{C4C8(\alpha)}$$

(7)

and

$$v_{s\beta} = v_{B4B8(\beta)} + v_{C4C8(\beta)}$$

(8)

Table 1: Levels generated in A-phase for different of pole voltages of inverter I and inverter II

| Pole voltage       | Pole voltage of                | VA4A8              | No.   |

|--------------------|--------------------------------|--------------------|-------|

| of inverter I      | inverter II v <sub>A2o</sub> ' |                    | of    |

| V <sub>A40</sub>   |                                |                    | level |

| 0                  | V <sub>dc</sub> /2             | $-V_{dc}/2$        | L1    |

| 0                  | $3V_{dc}/8$                    | $-3V_{dc}/8$       | L2    |

| 0                  | V <sub>dc</sub> /4             | $-V_{dc}/4$        | L3    |

| 0                  | V <sub>dc</sub> /8             | $-V_{dc}/8$        | L4    |

| 0                  | 0                              | 0                  | L5    |

| V <sub>dc</sub> /8 | 0                              | V <sub>dc</sub> /8 | L6    |

| V <sub>dc</sub> /4 | 0                              | V <sub>dc</sub> /4 | L7    |

| $3V_{dc}/8$        | 0                              | $3V_{dc}/8$        | L8    |

| V <sub>dc</sub> /2 | 0                              | V <sub>dc</sub> /2 | L9    |

Table 2: States of top switches of two-level inverters for Aphase in inverter I

| S <sub>a1</sub> | $S_{a2}$ | S <sub>a3</sub> | $S_{a4}$ | V <sub>A40</sub>   | Case |

|-----------------|----------|-----------------|----------|--------------------|------|

| 0               | 0        | 0               | 0        | 0                  |      |

| 1               | 0        | 0               | 0        | 0                  |      |

| 0               | 1        | 0               | 0        | 0                  |      |

| 1               | 1        | 0               | 0        | 0                  | A    |

| 0               | 0        | 1               | 0        | 0                  |      |

| 1               | 0        | 1               | 0        | 0                  |      |

| 0               | 1        | 1               | 0        | 0                  |      |

| 1               | 1        | 1               | 0        | 0                  |      |

| 0               | 0        | 0               | 1        | V <sub>dc</sub> /8 |      |

| 1               | 0        | 0               | 1        | V <sub>dc</sub> /8 | В    |

| 0               | 1        | 0               | 1        | V <sub>dc</sub> /8 | ь    |

| 1               | 1        | 0               | 1        | V <sub>dc</sub> /8 |      |

| 0               | 0        | 1               | 1        | V <sub>dc</sub> /4 | C    |

| 1               | 0        | 1               | 1        | V <sub>dc</sub> /4 | С    |

| 0               | 1        | 1               | 1        | $3V_{dc}/8$        | D    |

| 1               | 1        | 1               | 1        | V <sub>dc</sub> /2 | Е    |

The space vectors of the two five-level inverters will take different locations. There are totally 729 location forming 384 sectors in vector diagram of the all inverter and this structure is identical to that of a conventional nine-level inverter.

## VI. Type Of Multicarrier PWM

Among modulation methods are performed for specific topology by considering many aspect such as output voltage THD and fundamental voltage.

The multicarrier based PWM schemes are classified mainly as level shifted PWM (LSPWM), Variable Frequency PWM (VF-PWM) and Carrier Overlapping PWM (CO-PWM).

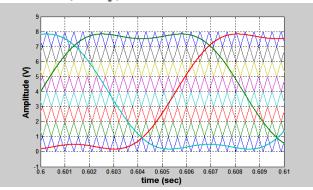

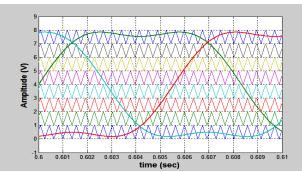

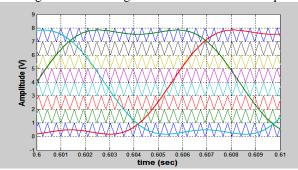

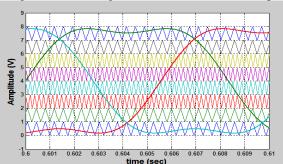

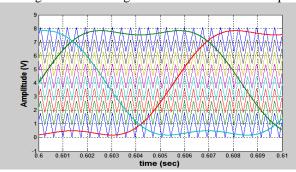

LSPWM is defined from the carrier wave disposition design presented by carrara et al [9]. For an N-level inverter this method required N-1 triangle carriers with same amplitude and frequency so that they completely take contiguous band. Three carrier disposition PWM technique are (i) Alternative Phase Opposition Disposition (APOD) shown in Fig. (2), where each carrier is phase shifted by 180° respectively. (ii) Phase Disposition (PD) shown in Fig. (3), where all carriers are in same phase.(iii) Phase Opposition Disposition (POD) illustrated in Fig.(4), where carriers above zero sinusoidal reference are 180°. The amplitude modulation index ma is equal

$$m_a = \frac{2V_m}{(N-1)V_c}$$

(9)

where v<sub>m</sub> is modulation amplitude while v<sub>c</sub> is carrier amplitude.

VF-PWM is used to balanced device switching for all of the levels where varying the frequency for the different triangle wave carrier bands as shown in Fig. (5). CO-PWM is carrier overlapping method illustrated by Fig. (6), N-1 carriers are disposed such that the bands they take overlap each other. The overlapping vertical magnitude between each carrier is  $v_C/2$ , where  $v_C$  is 1.8 V and the amplitude modulation index (ma) in this method is defined as

$$m_a = \frac{V_m}{\binom{N}{2} \cdot V_C} \tag{10}$$

The reference waves is used for the proposed work are

$$v_a^* = V_m \sin(\omega t) + 0.2 V_m \sin(3\omega t) + 4 V_c$$

(11)

$$v_a^* = V_m \sin(\omega t) + 0.2 V_m \sin(3\omega t) + 4V_C$$

(11)

$$v_b^* = V_m \sin(\omega t - \frac{2\pi}{3}) + 0.2 V_m \sin(3\omega t) + 4V_C$$

(12)

$$v_c^* = V_m \sin(\omega t + \frac{2\pi}{3}) + 0.2 V_m \sin(3\omega t) + 4V_c$$

(13)

Fig.2 Carrier arrangement for APODPWM technique.

Fig.3 Carrier arrangement for PDPWM technique.

Fig.4 Carrier arrangement for PODPWM technique.

Fig.5 Carrier arrangement for VF-PWM technique.

Fig.6 Carrier arrangement for CO-PWM technique.

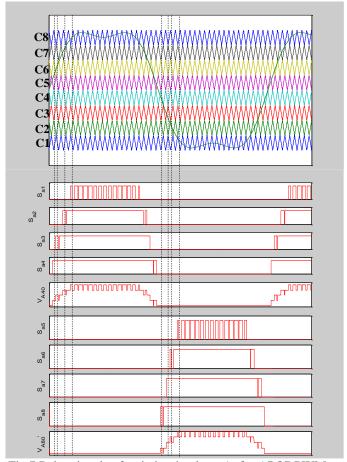

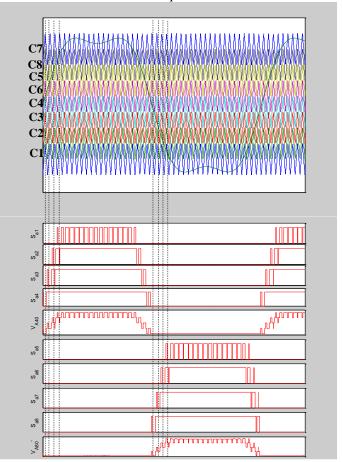

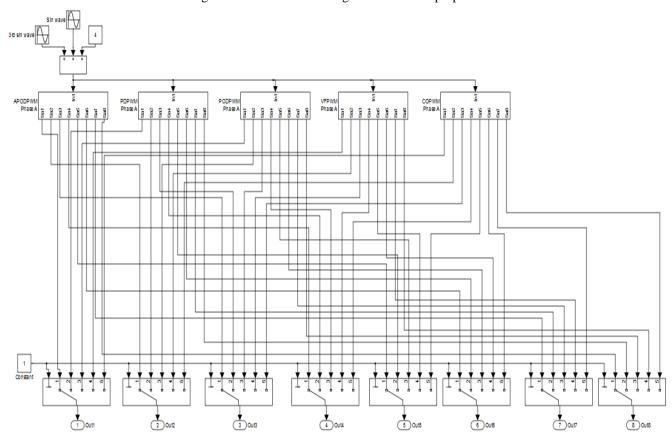

For the nine-level inverter, eight triangular waves carriers are used with modulating voltage wave and each carrier is compared with modulating signal and the result can be used to control of one three-phase bridge. Figures 7 and 8 are illustrated timing pulse generation and pole voltage for two modulation (APODPWM and COPWM) methods. The simulation of the 9-level is done using MATLAB model software. In this paper we used four threephase bridge in each side connected in cascade across open end winding induction motor with two voltage sources as input and IGBTs are used as switches illustration in Fig.9. Three subsystem block (one block for each phase) can be generation timing pulses for the switches, the output from these three subsystem are connected to multiport switches block to choose the one modulation techniques that used in this paper as shown in Fig.10.

Fig.7 Pulse signals of switches in phase A for APODPWM technique.

Fig.8 Pulse signals of switches in phase A for COPWM technique.

Fig.9 Simulation block diagram of circuit proposed.

Fig.10 Simulation block diagram of pulse generation in phase A.

## VII. Simulation Result

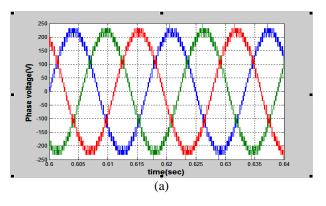

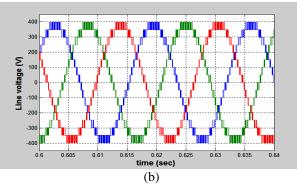

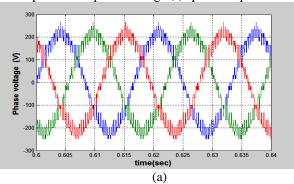

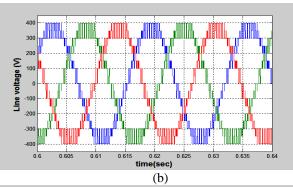

The nine level inverter is modeled in SIMULINK/MATLAB using power system set. Simulations are performed for different modulation technique and different values of amplitude modulation index  $m_a$  ranging from 0.2-0.95. The Simulink model for a motor of  $380\ V$  , 4-pole and,  $60\ Hz.$  The line voltage, phase voltage, pole

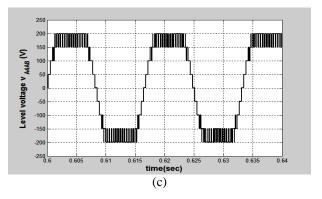

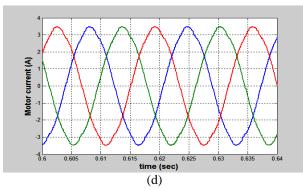

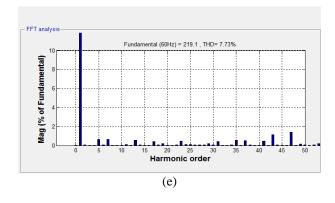

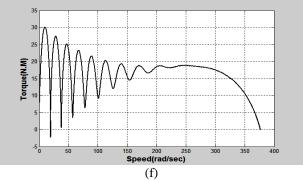

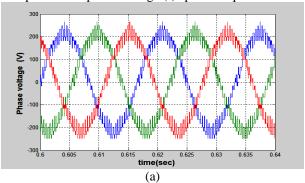

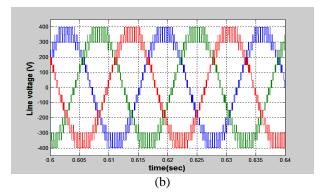

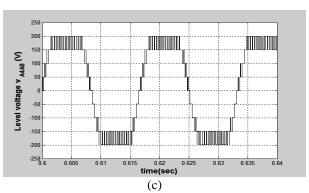

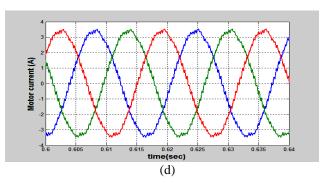

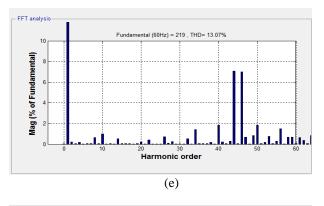

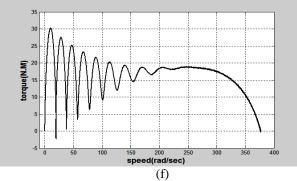

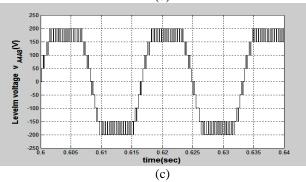

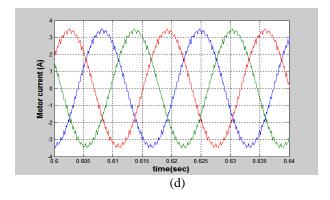

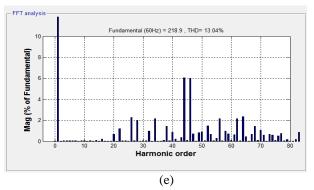

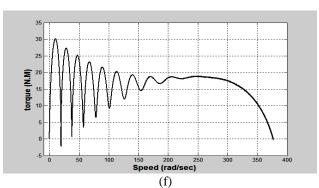

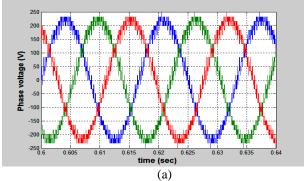

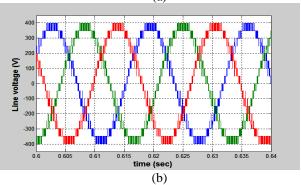

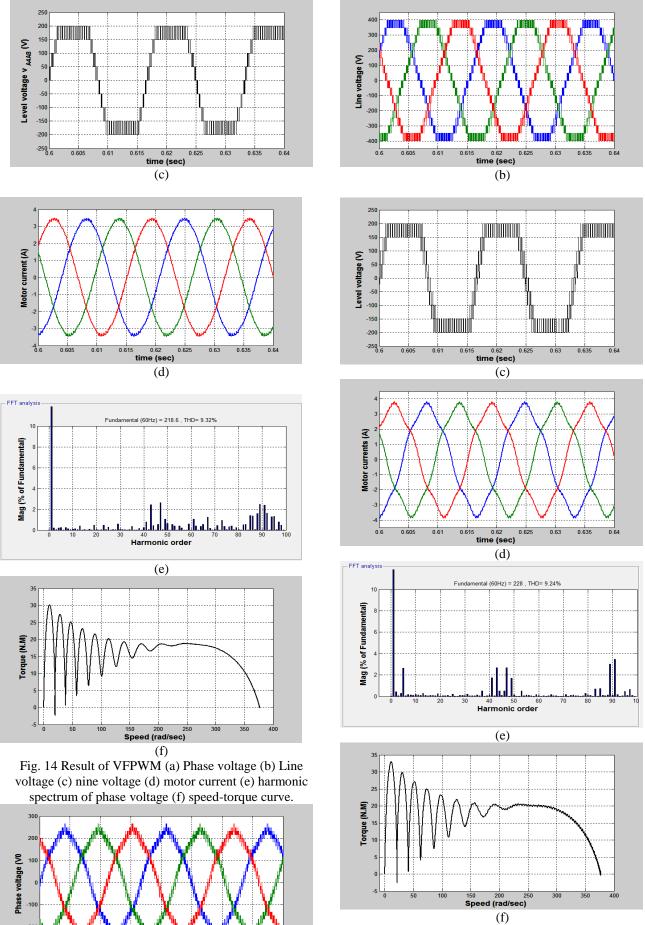

voltage, nine level voltage, motor current, harmonic spectrum of phase voltage and speed-torque curve for different modulation techniques are shown in Figs. (11-15).

Fig. 11 Result of PDPWM (a) Phase voltage (b) Line voltage (d) nine voltage (d) motor current (e) harmonic spectrum of phase voltage (f) speed-torque curve.

Fig. 12 Result of PODPWM (a) Phase voltage (b) Line voltage (c) nine voltage (d) motor current (e) harmonic spectrum of phase voltage (f) speed-torque curve.

(f)

Fig. 13 Result of APODPWM (a) Phase voltage (b) Line voltage (c) nine voltage (d) motor current (e) harmonic spectrum of phase voltage (f) speed-torque curve.

0.61

0.615

(a)

0.63

Fig. 15 Result of COPWM (a) Phase voltage (b) Line voltage (c) nine voltage (d) motor current (e) harmonic spectrum of phase voltage (f) speed-torque curve.

Among all different modulation techniques, PDPWM provides minimum amount of harmonic content but COPWM modulation provide high fundamental voltage.

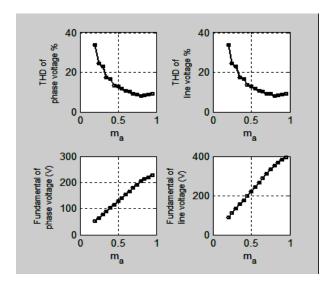

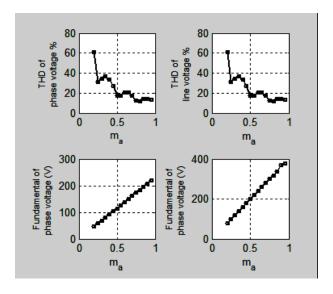

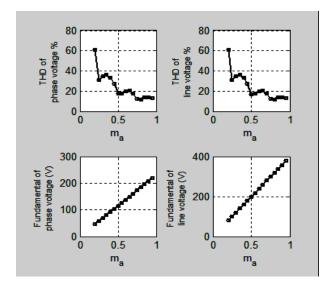

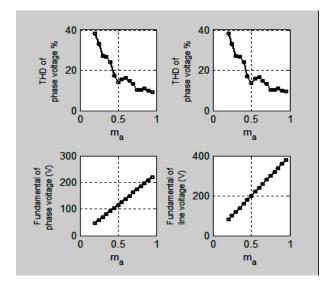

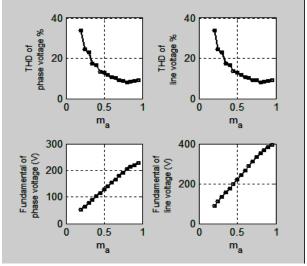

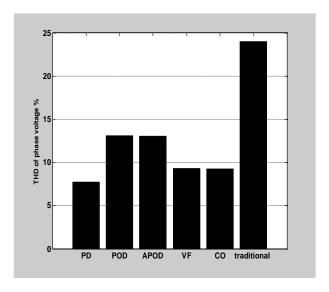

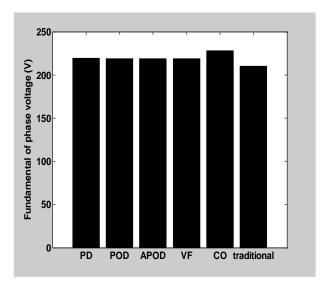

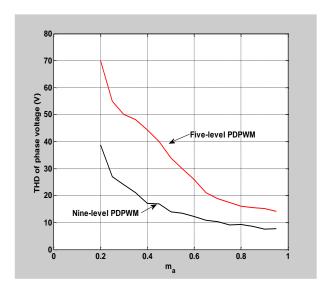

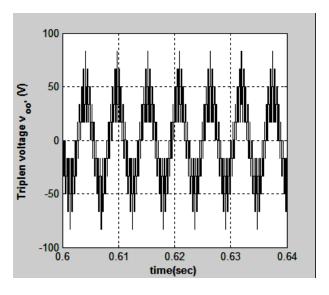

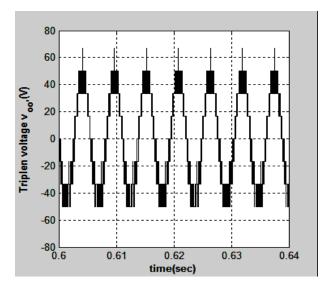

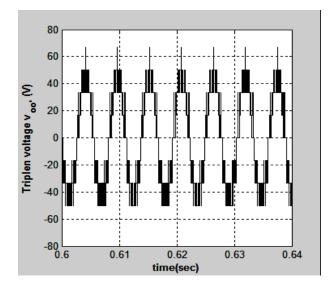

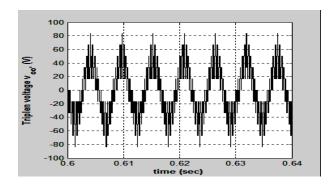

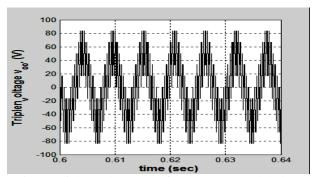

The different relationship between THD , fundamental voltage and modulation index are shown in Figs. (16-20). The THD and fundamental voltage comparison at modulation index 0.95 for various carrier based PWM modulation techniques for nine-level inverter are shown in Figs.(21-22). Comparator between nine and five levels in PDPWM technique is shown in Fig. 23 illustrated low harmonic with increase number of level voltage. Figs. (24-28) show the triplen voltage content  $V_{\rm OO}$  (measured between O and O' nodes in Fig. 1) in each modulation techniques.

Fig. 16 Different relationship with modulation index for PDPWM modulation.

Fig. 17 Different relationship with modulation index for PODPWM modulation.

Fig. 18 Different relationship with modulation index for APODPWM modulation.

Fig. 19 Different relationship with modulation index for VFPWM modulation.

Fig. 20 Different relationship with modulation index for COPWM modulation.

Fig.21 Relationship of THD for different modulation techniques.

Fig.22 Relationship of fundamental phase voltage for different modulation techniques.

Fig.23 Relationship of THD and modulation index for five and nine level in PDPWM.

Fig.24 Triplen voltage  $V_{\text{OO}}$  for PDPWM modulation.

Fig.25 Triplen voltage  $V_{OO'}$  for PODPWM modulation.

Fig.26 Triplen voltage  $V_{\text{OO}'}$  for APODPWM modulation.

Fig.27 Triplen voltage V<sub>OO'</sub> for VFPWM modulation.

Fig.28 Triplen voltage V<sub>OO'</sub> for COPWM modulation.

#### **VIII. Conclusion**

In this paper, number of multilevel PWM strategy for chosen nine-level inverter fed open end winding induction motor (OEWIM) have been analysis and simulation results are presented for different modulation indices ranging from 0.25-0.95. Abundance performance factor like %THD and root mean square of fundamental voltage have been evaluated, presented and analyzed. Among all different modulation techniques, PDPWM provides minimum content of harmonic content but COPWM modulation provide maximum value fundamental voltage.

#### IX. REFERENCES

- [1] N. Yousefpoor, S. H. Fathi, N. Farokhnia, and H. A. Abyaneh, "THD Minimization Applied Directly on the Line-to-Line Voltage of Multilevel Inverters" IEEE Transactions on Industrial Electronics, Vol. 59, no.1, pp. 373-380, Jan. 2012.

- [2] A. Nami, F. Zare, A. Ghosh, and F. Blaabjerg,"A Hybrid Cascade Converter Topology With Series-Connected Symmetrical and Asymmetrical Diode-Clamped H-Bridge Cells" IEEE Transactions on Power Electronics, Vol. 26, no. 1,pp.51-65, Jan. 2011.

- [3] A. L. Batschauer, S A. Mussa, and M.L. Heldwein, "Three-Phase Hybrid Multilevel Inverter Based on Half-Bridge Modules" IEEE Transactions on Industrial Electronics, Vol. 59, no. 2, pp. 668-678, Feb. 2012

- [4] K. K. Mohapatra, K. Gopakumar, V. T. Somasekhar and L. Umanand," A Harmonic Elimination and Suppression Scheme for an Open-End Winding Induction Motor

- Drive" IEEE Transactions on Industrial Electronics, Vol. 50, no. 6, pp.1187-1198, Dec. 2003.

- [5] J. Li, J. Liu, D. Boroyevich, P. Mattavelli, and Y. Xue, "Three-level Active Neutral-Point-Clamped Zero-Current-Transition Converterfor Sustainable Energy Systems" IEEE Transactions on Power electronics, Vol. 26, no. 12, pp.3680-3693 Dec. 2011.

- [6] K.C. Sekhar, and G.T. R. Das, "Multilevel Voltage Space Phasor Generation for an Open-end Winding Induction Motor Drive" Int. Journal of Electrical and Electronic Systems Research, Vol.1, pp.1-10, June 2008.

- [7] J. Álvarez, Ó. López, F. D. Freijedo, and J. Doval-Gandoy, "Digital Parameterizable VHDL Module for Multilevel Multiphase Space Vector PWM" IEEE Transactions on Industrial Electronics, Vol. 58, no. 9, pp.3946-3956, Sep. 2011.

- [8] S. Pradabane, N. V. Srikanth and, B. L. Narasimharaju "A New Alternate Fixed-Bias Inverter SVPWM Scheme for Open-End Winding Induction Motor Drive" International Review of Electrical Engineering (I.R.E.E.), Vol. 9, No. 1, ISSN 1827- 6660, pp.1-6, Jan. Feb. 2014.

- [9] A. Nabae, I. Takahashi, and H. Akagi, "A new neutral-point-clamped PWM inverter," *IEEE Trans. Industry Applications*, vol. IA-17, no. 5, pp. 518-523, Sept. 1981.